병렬 처리 방법에는 명령어 단계 병렬 처리와 프로세서 단계 병렬 처리가 있다.

명령어 단계 병렬 처리는 컴퓨터에서 초당 더 많은 명령어를 실행하기 위해 개별 명령 내에서 병렬화가 사용된다.

프로세서 단계 병렬 처리는 한 가지 문제에 대해 여러 개의 프로세서가 동시에 작동 한다.

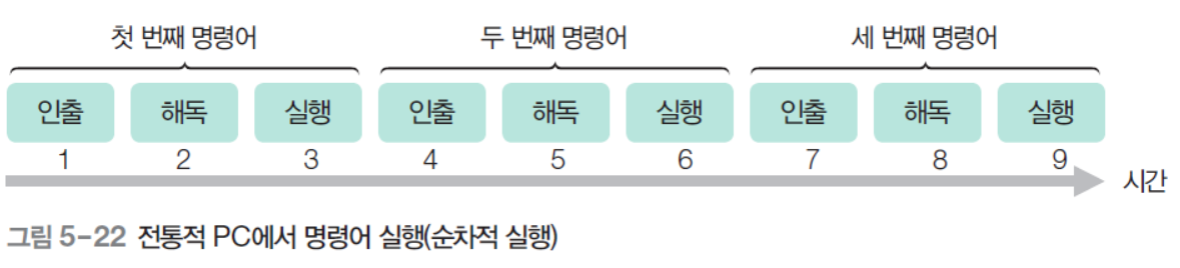

모든 프로세서 제어 장치는 기본적으로 '명령어 인출 -> 명령어 해독 -> 명령어 실행' 순서 대로 명령을 수행한다.

반면, 현대 대부분의 프로세서에서는 파이프 라이닝(pipelining) 기술을 사용하여 명령을 싱핸한다.

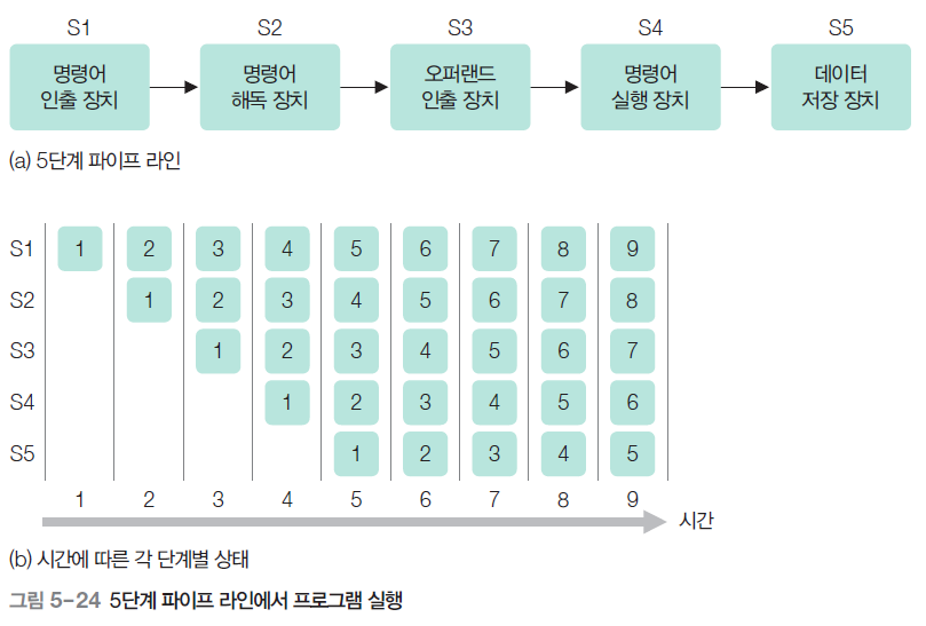

파이프 라이닝은 명령 하나를 단계 여러 개로 나누어 각각을 독립적인 장치에서 동시에 실행하는 기술이다.

5단계 파이프라인

1단계: 메모리에서 명령어를 인출, 필요할 때까지 버퍼에 저장

2단계: 명령어를 해독하고 명령어 형태를 결정, 필요한 피연산자 결정

3단계: 레지스터 또는 메모리에서 피연산자 결정

4단계: 명령어 연산 수행

5단계: 적절한 레지스터에 저장

장치 5개가 서로 독립적으로 작동하고 각각의 명령이 순서대로 각 장치를 이동하며 실행된다면 실행 시간은 훨씬 단축된다.

파이프 라이닝을 사용하면 지연 시간(명령어를 싱행하는 데 걸리는 시간)과 프로세서 대역폭(CPU의 MIPS, Million Instructions Per Second 수) 간 균형을 유지할 수 있다.

- 한 사이클에 소요되는 시간: Tns

- 파이프라인의 단계: n

- 전체 걸리는 시간: nTns

이론저으로는 파이프 라인 단계 수만큼 빨라지지만 실제로는 이를 방해하는 요소들이 있다. 이를 해저드라고 하며 대표적으로 데이터 해저드, 제어 해저드, 구조적 해저드가 있다.

1. 데이터 해저드(data hazard)

데이터 해저드란 파이프 라인에서 앞서가는 명령의 ALU 연산 결과를 레지스터에 기록하기 전에 다른 명령에 이 데이터가 필요한 상황을 의미한다.

이것을 데이터 의존성(data dependancy)이라고 한다.

즉, 앞의 명령 결과가 다음 명령 입력으로 사용될 때 파이르 라인 시스템에서 문제가 발생한다.

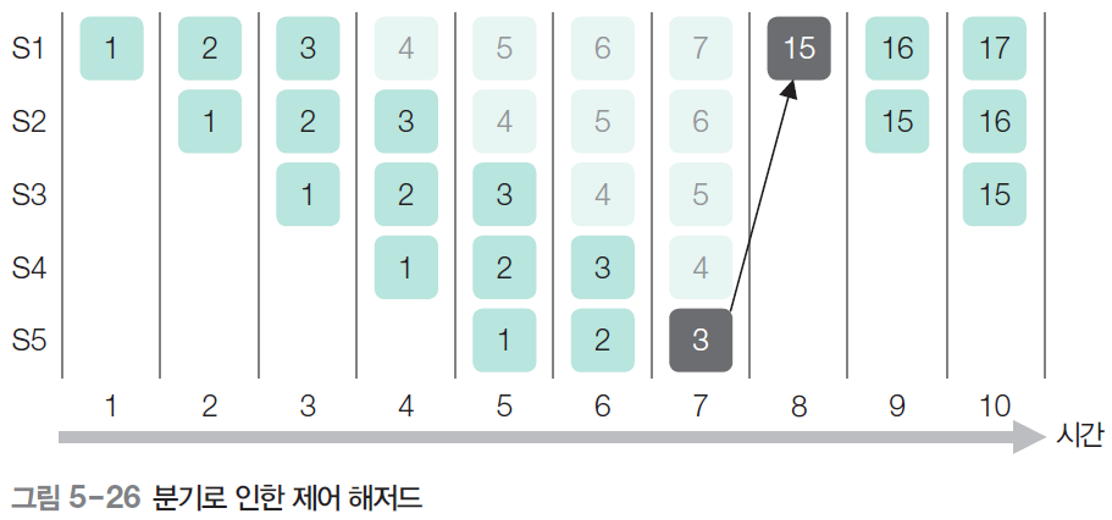

2. 제어 해저드(control hazard)

제어 해저드는 파이프 라인 CPU 구조의 분기 명령이 실행될 때 발생한다.

이때 이미 파이프 라인에 적재되어 실행되고 있는 이어지는 다른 명령들이 더 이상 필요가 없어지면서 발생한다.

해결 방법으로는 지연 슬롯(delay slot)을 넣고 분기 목적지 주소를 계산하는 과정을 파이프 라인 속에 넣는 것이다.

지연 슬롯은 NOP나 분기 명령과 무관한 명령을 끼워 넣는 것이다.

이 방법은 컴파일러나 프로그래머가 프로그램 순서를 바꾸는 것이다.

지연을 지연 분기라고 하며 다른 방법으로 분기 예측 알고리즘을 이용하는 경우도 있다.

3. 구조적 해저드(structural hazards)

구조적 해저드는 서로 다른 단계에서 실행되는 명령이 컴퓨터 내의 장치 하나를 동시에 사용하려고 할 때 발생한다.

예를 들어, 명령어 인출과 오퍼랜드 인출이 동시에 발생하는 경우, 명령 2개가 동시에 메모리에 가서 명령과 데이터를 가져와야 하는데, 인출 과정이 모두 같은 장치들(bus, memory 등)을 사용하므로 충돌이 발생한다.

또는 CPU내의 장치인 ALU를 명령 2개가 동시에 사용해야 할 때 충돌이 발생할 수 있다.

인출 과정에서 메모리 충돌을 해결하기 위해서는 하버드 구조(havard architecutre)를 사용하거나, 분리 캐시를 사용하여 충동을 피하게 만들어 주면 된다.

하버드 구조는 메모리를 프로그램 메모리와 데이터 메모리를 완전 분리시킨 구조이므로 명령어 인출과 데이터 인출 과정에서 충돌을 원천적으로 방지한다. 이는 RISC 프로세서에서 많이 사용되는 구조다.

분리 캐시는 인텔 계열 프로세서의 L1 캐시에서 사용하는 구조로, L1 명령어 캐시와 L1 데이터 캐시로 구분하여 사용한다. 그러나 이때 명령어 2개가 통시애 키시 미스가 발생하면 충돌이 발생할 수 있다.

또한 동일한 장치를 동시 사용하여 충돌을 해결하는 방법은 장치(CPU내에 2개의 ALU)를 하나 더 두는 것이다.

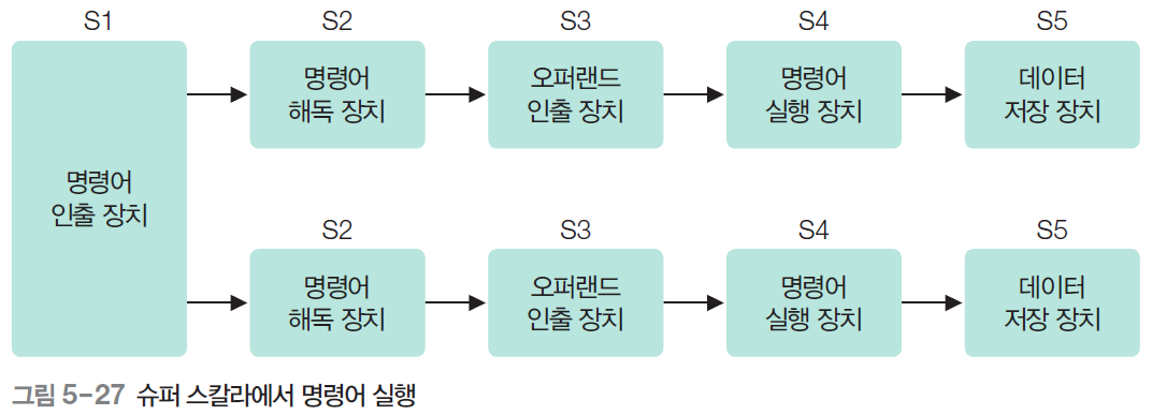

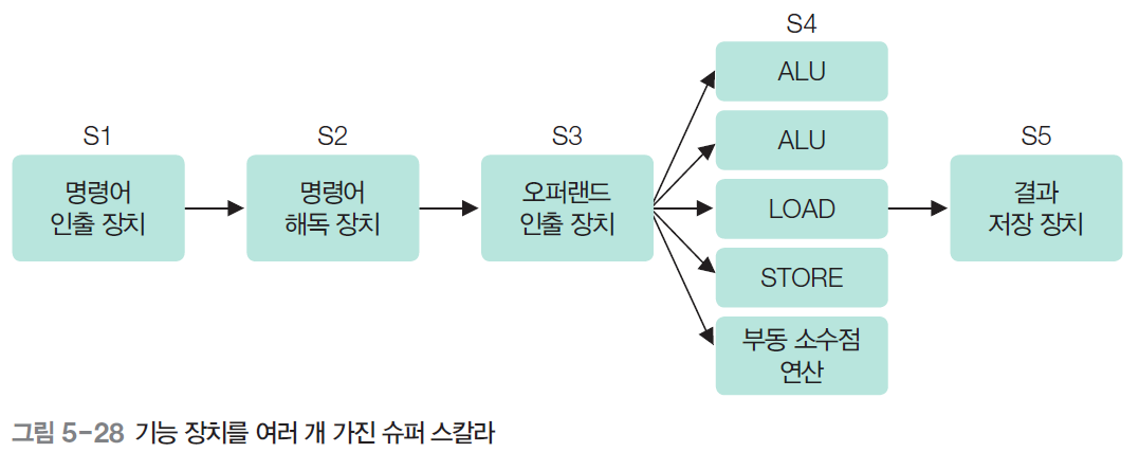

슈퍼 스칼라

하나의 프로세서 안에 2개 이상의 파이프 라인 탑재

2중 파이프 라인 프로세서의 가능한 한 가지 구조인 슈펴 스칼라는 명령어 인출 유닛 하나가 명령어 쌍을 함께 가져와서 각 명령어를 다른 파이프 라인에 배치하고 개별 ALU를 가지고 병렬 작업을 한다.

병렬로 실행되기 위해 명령 2개는 자원을 사용할 때 충돌하지 않아야 하며, 둘 중 어느 명령도 다른 명령의 결과에 의존하지 않아야 한다.

정해진 규칙은 명령어 한 쌍이 서로 호환되어 병렬로 실행될 수 있는지 여부를 결정한다.

명령어 한 쌍이 충분히 단순하지 않거나 호환되지 않는 경우, 첫 번째 명령만 실행된다.

두번 째 명령은 멈추어 있다가 다음 명령과 짝을 지어 실행된다.

명령어는 항상 순서대로 수행된다.

슈퍼 스칼라 프로세서라는 아이디어는 S3이 S4 단계보다 훨씬 빠르게 명령을 실행 가능하다는 것이다.

'IT > 컴퓨터구조' 카테고리의 다른 글

| 최신 컴퓨터 구조: 2장 연습문제 (0) | 2023.04.16 |

|---|---|

| 최신 컴퓨터구조: 1장 연습문제 (1) | 2023.04.16 |

| 컴퓨터구조: 프로세서 제어 (0) | 2023.04.16 |

| 컴퓨터 구조: 명령어 사이클 (0) | 2023.04.16 |

| 컴퓨터 구조: 제어 장치의 종류 (0) | 2023.04.16 |